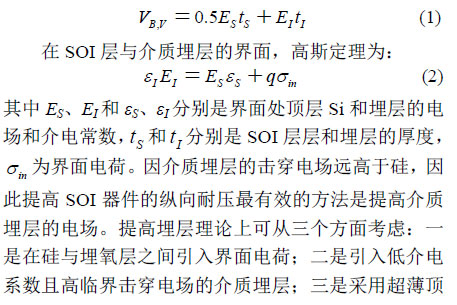

摘要:提高纵向耐压是SOI高压器件之关键,作者及科研团队总结出SOI高压器件介质场增强ENDIF(ENhanced DIelectric layer Field)理论与技术,通过增强介质埋层电场提高SOI器件的击穿电压。本文给出增强介质埋层电场的三项技术:在埋层上界面引入电荷;降低埋层介电系数;采用超薄顶层硅。基于ENDIF,提出并研制系列介质场增强SOI高压器件:电荷型SOI高压器件,低k和变k埋层SOI高压器件;薄硅层阶梯漂移区SOI高压器件,建立相应的耐压模型,并研制出耐压高于600V的几种SOI LDMOS。

关键词:SOI 高压ENDIF

1. 引言

SOI器件的介质埋层阻止了耗尽层向衬底扩展,故其纵向耐压低,这限制了SOI高压集成电路的应用,为此,国内外众多学者提出了一系列新结构以提高SOI高压器件的纵向耐压[1-4]。迄今,国际上没有一个统一的理论以指导SOI高压器件的纵向耐压设计。本文综述SOI横向高压器件的耐压问题,从耐压理论、器件结构和耐压解析模型几方面进行研究。提出SOI高压器件介质场增强(ENhanced DIelectric layer Field,ENDIF)理论与技术,获得介质层电场和纵向耐压的统一解析式[5-6];基于此,提出系列SOI高压器件新结构,建立耐压模型,并实验ENDIF理论与技术[7-11]。

2. 绝缘体上硅的介质场增强(ENDIF)

基于SOI器件介质层电场临界化的思想,提出SOI高压器件介质场增强理论,通过增强介质埋层的电场而提高SOI器件的纵向击穿电压。

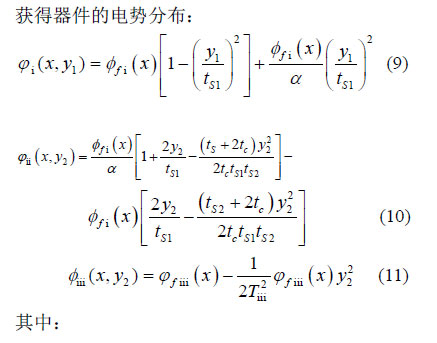

SOI器件采用结终端技术和RESURF技术以改善横向击穿电压,器件击穿电压由纵向击穿决定,在一维近似下,器件击穿电压写为:

3. 介质场增强SOI高压器件

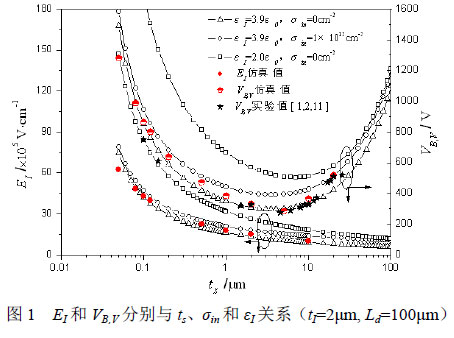

3.1 双面电荷槽SOI高压器件[7]

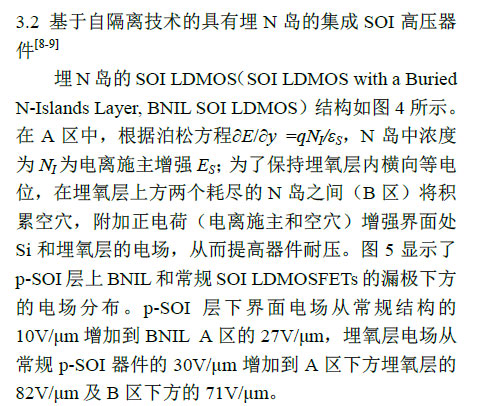

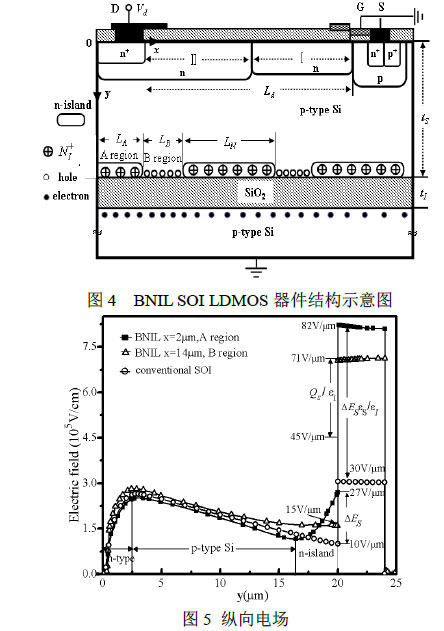

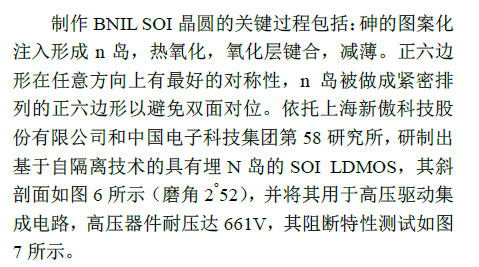

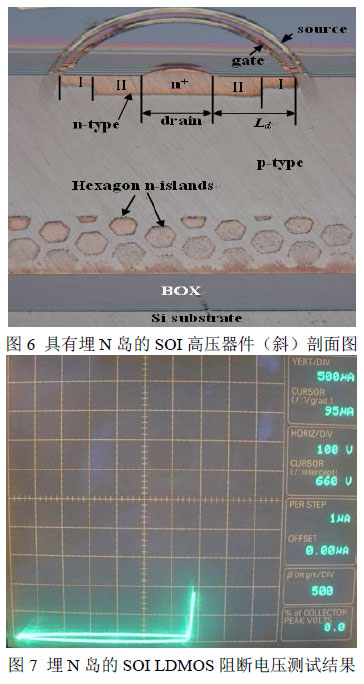

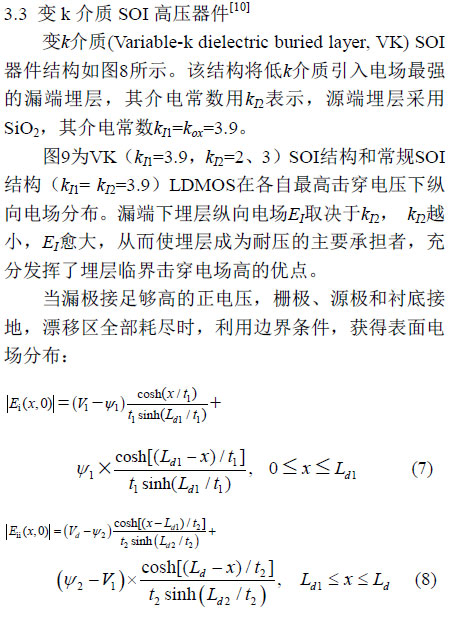

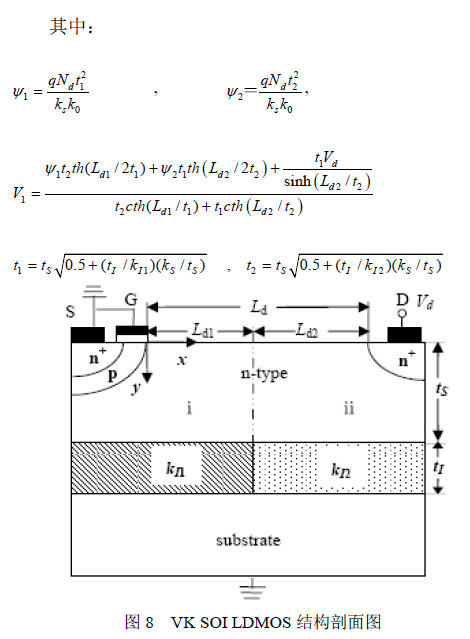

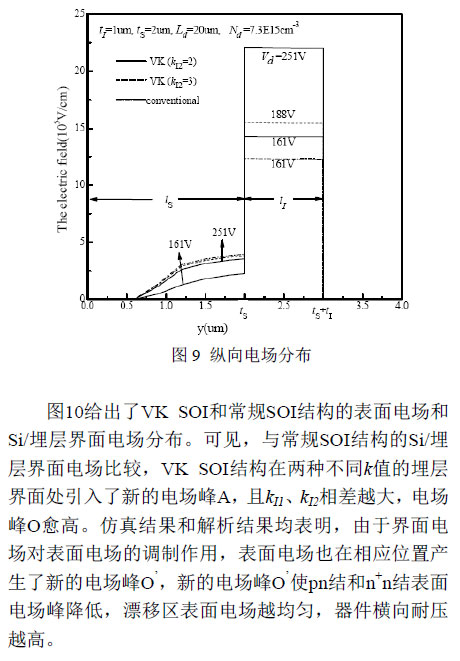

双面槽(Double-sided Trenches,DT) SOI器件结构和槽内电荷分布如图2所示。该结构在埋氧层的上下表面引入介质槽。当器件处于反偏状态时顶部槽底发生反型,反型层电荷被束缚在槽内,埋氧层下表面产生感生电荷。双面槽内的电荷增强埋氧层电场而提高器件耐压。

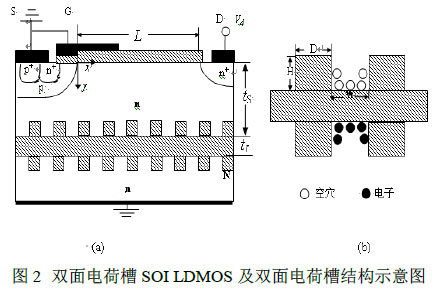

与中国电子科技集团第24研究所共同开发非平面埋氧层SOI材料制备工艺,并在20μm的SOI层和1μm的埋氧层上研制出730V的SOI LDMOS器件。双面电荷槽SOI材料的剖面SEM照片和SOI LDMOS阻断特性测试结果如图3所示。

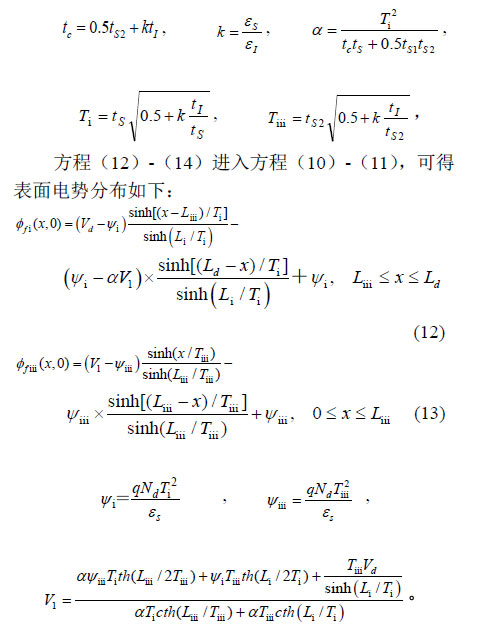

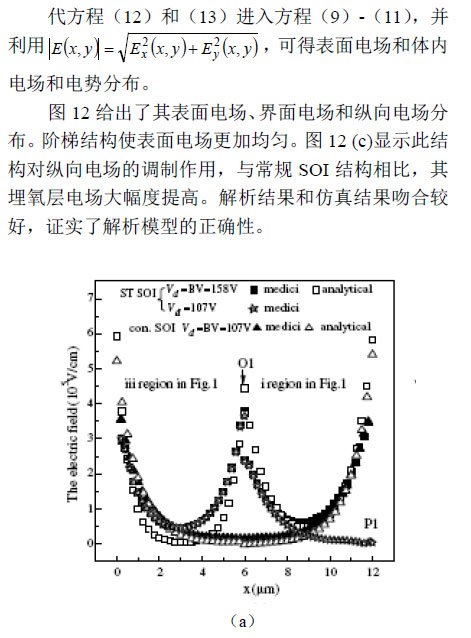

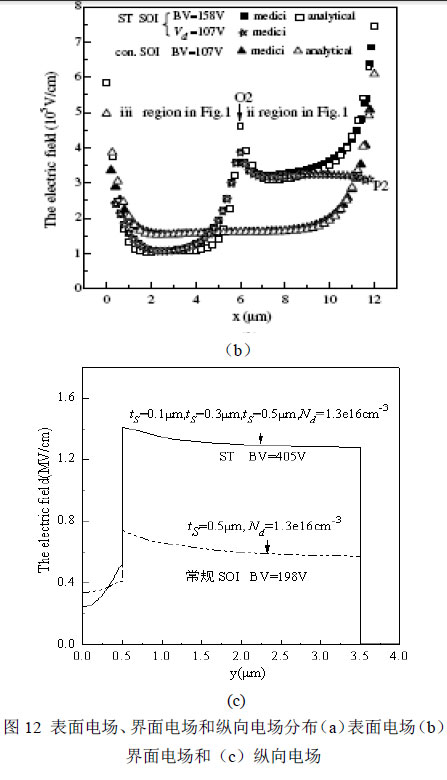

3.4 阶梯漂移区SOI高压器件及其解析模型[11]

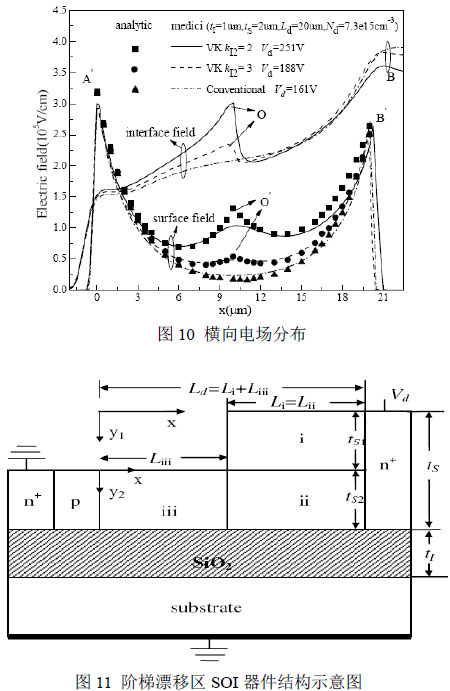

图11为阶梯漂移区(Step Drift Region SOI,SDR)SOI器件结构示意图。与常规SOI结构相比,阶梯漂移区对横向电场的调制作用使表面电场在阶梯处出现新的电场峰,表面电场更加均匀,因而提高器件的横向击穿电压;同时,漂移区电场又调制了埋氧层电场分布,从而增强了埋氧层电场,提高了器件的纵向击穿电压;漂移区浓度较高,降低了器件的比导通电阻。

4.结论

本文总结SOI高压器件介质场增强ENDIF理论与技术,通过增强介质埋层电场提高击穿电压,并给出三项增强介质场的技术:在埋层上界面引入电荷,降低埋层介电系数及采用超薄顶层硅。基于ENDIF理论,提出系列介质场增强SOI高压器件结构,并给出其中部分新结构的解析模型或实验结果。

参考文献:

[1] S. Merchant, E.Arnold, H. Baumgart. Realization of High Breakdown Voltage (>700V)in Thin SOI Devices [J], Proc.3rd Int. Symp. Power Semiconductor Devices and IC’s (Baltimore, USA), 1991, p.31.

[2] A.Nakagawa, N.Yasuhara and Y.Baba. Breakdown Voltage Enhancement for Devices on Thin Silicon Layer/Silicon Dioxide Film [J], IEEE Tran. Electron Devices, 1991, 38(7) ,p. 1650.

[3] Kapels H, Plikat R and Silber D. Dielectric Charge Traps. A New Structure Element for Power Devices [J], Proc. IEEE ISPSD, 2000, p.205.

[4] Yufeng Guo, Zhaoji Li, Xiaorong Luo, et al. New Structure and Breakdown Model of High Voltage SOI Devices with the Step Buried-oxide Fixed Charges [J], Chinese Journal of Semiconductors, 2004, 25(12), p. 1695.

[5] Bo Zhang, Zhaoji Li, Shengdong Hu, and Xiaorong Luo,field enhancement for dielectric layer of

high-voltage devices on silicon on insulator, IEEE Tran. Electron Devices, 2009, 56(10), p.2327.

[6] Zhaoji Li, Bo ZHANG, Xiaorong Luo, Shengong Hu, Jian Fang, Zehon Li, Ming Qiao and Yufeng Guo. The Rule of Field Enhancement for Buried Dielectric Layer of SOI High Voltage Devices [J]. International Conference on Communications, Circuits and Systems (Fukuok, Japan), 2007, p.1320.

[7] Xiaorong Luo, Bo Zhang, Zhaoji Li, A Novel 700V SOI LDMOS with Double-side Trench [J], IEEE Electron Device Lett, 2007, 28(5), p. 422.

[8] Xiaorong Luo, Tianfei Lei, Bo Zhang, Zhaoji Li, et al. A high-voltage LDMOS compatible with high voltage integrated circuits on p-type SOI layer [J], IEEE Electron Device Letters, 2009, 30(10), p. 1093.

[9] Xiaorong Luo, Bo Zhang, Tianfei Lei, Florin Udrea, et al. Numerical and Experimental Investigation on a Novel High Voltage (>600V) SOI LDMOS in the self-isolation HVIC [J], IEEE Tran. Electron Devices, 2010, 57(11), 3033.

[10] Xiaorong Luo, Bo Zhang, Zhaoji Li, A new structure and its analytical model for the electric field and breakdown voltage of SOI high voltage device with variable-k dielectric buried layer[J], Solid-State Electron, 2007,51(3), p. 493.

[11] Xiaorong Luo, Wei Zhang,Bo Zhang, et al. . Semiconductor Science and technology, 2008, 23 (3):No.035028.

[12] R. Van Overstraeten, H. De Man, Measurement of the ionization rates in diffused silicon p-n junctions[J], Solid-State Electron, 1970, 13(5