沟槽栅FS-IGBT 器件形貌结构的开发

饶祖刚

(单位:天津中环半导体股份有限公司)

摘 要:近年来随着IGBT器件技术的快速发展,采用沟槽栅和场终止(FS)的器件结构成为新一代技术的亮点。本文

提出了一种新型的沟槽栅制造方法和一种超薄硅片加工方法,并对器件的终端结构进行了讨论;也探讨了在沟槽栅

FS-IGBT器件研发过程中遇到的器件形貌结构上的问题,分析了这些问题所发生的原因,提出了针对这些问题的解决方案,

实现了沟槽栅FS-IGBT器件的形貌结构。文中所阐述的问题均来自于研发实践,所确定的解决方案也在器件研发过程中得到了验证。

关键词: IGBT 沟槽栅 场终止 超薄片

The development of a trench gate field stop IGBT device structure

Rao Zugang

(Unit: Tianjin Zhonghuan Semiconductor Co., Ltd)

Abstract: Recent years, with the rapid development of IGBT device, the trench gate field stop device structure has become a highlight as a new technology. A new novel trench gate process and a new super thin wafer process are roposed, andthe device termination structure is discussed. The profile issues which arose from the trench gate field stop IGBT device development are also discussed, the causes are analyzed and the solutions are proposed. The issues described in this paper are all from the R&D practice and the solutions are all verified in the trench gate field stop IGBT device development.

Keywords:IGBT; Trench gate; Field stop; Super thin wafer

1 引 言

近年来随着IGBT器件技术的快速发展,IGBT器件作为一种新型电力电子器件以其大功率、高频率的 优势逐步取代传统器件,在消费电子、工业控制、汽车电子、计算机和通信领域中得到了广泛的应用,也成为新能源、高压输变电、机车牵引等国家战略新兴产业中的关键器件。据IC Insights预测,从2010 年到2015年,IGBT分立器件的销售年平均增长率将为6.5%达到2015年的12亿美元,IGBT模块的销售复合年平均增长率将为7%达到2015年的32亿美元。然而我国IGBT器件大规模的研发和产业化才刚刚起步,绝大部分IGBT器件仍依赖于从国外进口,IGBT器件的研发和产业化成为了行业内的一个热点,国家也跟进了很多鼓励政策来加速这一进程。

IGBT及其器件技术的研究和发展已经有40多年的历史了。在前20年的时间里,该器件一直处于结构的提出、工作模式的发现和商业化的实现等奠基工作之中。1968年日本三菱(Mitsubishi)株式会社的K.Yamagami首次提出了IGBT器件结构,并在日本申请了专利[1]。在该专利中,他在类似现在常规VDMOS器件的基础上,将重掺N型漏区以P型重掺区替代,并在该重掺的P型区内选择性地重掺N型杂质形成器件。

1978年美国通用电气(GE)公司研发中心的B. J. Baliga在实验中发现了器件的IGBT工作模式,在他1979年发表的文献中,称其为“以P型阳极区替代漏区的V型MOSFET器件”[2]。1982年美国无线电(RCA)公司的H. W. Becke和C. F. Wheatley等人申请了一项名为“带阳极区的功率MOSFET”发明专利[3],该专利描述的器件结构与现在典型的平面IGBT器件结构基本相同,发明中还提出降低漂移区的电导率,增设高电导率的具有场终止作用的缓冲层的改善结构,该专利被誉为是“IGBT具有开创性的专利”[4]。然而,这时期的IGBT器件因关断速度慢和闩锁效应的存在限制了其应用。1983年B. J. Baliga证实了使用电子辐照缩短漂移区的少子寿命,可以提高IGBT的关断速度,并获得了200纳秒关断时间的成果[5]。1984年日本东芝(Toshiba)株式会社的A. Nakagawa等对IGBT器件做了进一步改进,在源区中增加了低阻的空穴通道。将开发出的1200伏75安培的IGBT样品用600伏稳定电压进行了短路测试,实现了25微秒的安全开关,取得了抑制闩锁效应的突出成果[6],并于1985年申请了美国专利[7]。在此基础上,1985年日本东芝(Toshiba)株式会社首次将1000伏25安培的IGBT器件产品推向了商业化[8]。

自此以后,二十多年IGBT器件技术和IGBT产品的应用都得到了突飞猛进的发展。IGBT器件技术的发展已经经历了好几代,从平面型IGBT器件到沟槽型IGBT器件[9],从PT型IGBT器件到NPT型IGBT器件[10]、FS型IGBT器件[11]和SPT型IGBT器件[12]、SPT+型IGBT器件[13]以及CSTBT型IGBT器件[14]等;在终端结构方面,从场限环(FLR)、场板(FP)到结终端扩展技术(JTE)、变掺杂技术(VLD)[15~16]等。随着一项项新技术的不断刷新,IGBT器件的性能也得到了不断的改善,采用沟槽栅和场终止(FS)结构的IGBT器件技术成为了新一代技术的亮点。为实现场终止(FS)结构,常用的方法是首先对硅片进行减薄处理,然后从硅片背面对硅片进行掺杂,电压越低硅片减得越薄。在IGBT器件的研发和产业化过程中,需要解决从器件设计、制造工艺、芯片测试、芯片封装、成品测试以及应用层面的诸多课题,其中芯片制造工艺的开发是一个重点,尤其是器件形貌结构的实现和器件内杂质分布的形成和控制。本文主要针对前者,即对器件形貌结构的开发进行了阐述。本文所阐述的方法和相关问题均来自于1200V沟槽栅FS-IGBT器件的研发实践,针对问题所确定的解决方案也在器件的研发过程中得到了验证。

2 器件形貌结构的开发

沟槽栅场终止(FS)器件形貌结构的开发主要包括三个方面:一是器件元胞形貌结构的开发,二是器件终端形貌结构的开发,三是超薄片的实现与超薄片工艺加工。

2.1 器件元胞形貌结构的开发

器件元胞的形貌结构由栅电极、层间绝缘层、接触孔、金属电极和钝化层组成。对于沟槽栅场终止(FS)器件,沟槽栅形貌结构的开发是器件元胞形貌结构开发的核心,之后再完成其它工序的加工。器件终端的形貌结构由复合场限环、复合场板、层间绝缘层和钝化层构成。

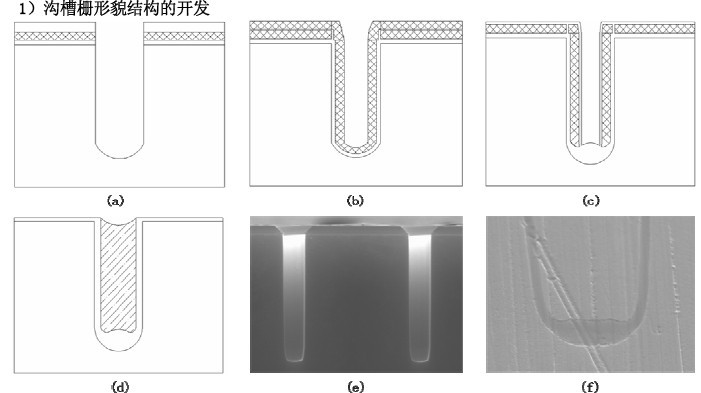

图1 新型沟槽栅制造方法下各阶段的形貌结构((a)ONO 硬掩膜与沟槽,(b)双层氮化硅结构,(c)沟槽LOCOS 结构,(d)沟槽栅结构,(e)开发出的沟槽,(f)开发出的沟槽栅底部形貌结构)

在沟槽栅FS-IGBT 器件形貌结构的开发过程中,我们提出了一种新型的沟槽栅制造方法。利用该方法可以制造出沟槽底部氧化硅薄膜厚、侧壁氧化硅薄膜薄的沟槽栅氧化硅薄膜结构,以实现器件栅耐压的提升,减小栅极与集电极间电容,加快开关速度的目的。该方法的制造过程是:在前层工艺的基础上,首先制备氧化硅-氮化硅-氧化硅(ONO)薄膜,并以该薄膜作为硬掩膜在芯片表面的元胞区刻蚀出沟槽(如图1(a)所示)。为了去除沟槽刻蚀产生的缺陷,进行了牺牲氧化和刻蚀,此次刻蚀同时也将ONO 薄膜最上层的氧化硅薄膜刻蚀干净。在此之后再氧化,低压生长氮化硅薄膜,这样在沟槽中硅的上层为氧化硅和氮化硅层,沟槽外硅片表面为氧化硅、氮化硅、氧化硅和氮化硅层(如图1(b)所示)。以反应离子刻蚀(RIE)方法将沟槽底部的氮化硅薄膜刻蚀干净,同时将沟槽外硅片表面上层的氮化硅薄膜刻蚀干净,并保持一定的过刻蚀,该过刻蚀不应将沟槽底部的氧化硅薄膜刻蚀干净,以免导致硅衬底损伤。之后对沟槽进行局部氧化(LOCOS),从而在沟槽底部生长一层厚的氧化硅薄膜(如图1(c))。将沟槽侧壁和沟槽外面硅片表面的氧化硅薄膜和氮化硅薄膜刻蚀干净,只在沟槽底部留下一层氧化硅薄膜。接下来进行了栅氧化和掺杂多晶硅填充,并回刻多晶硅形成了本制造方法下的沟槽栅结构(如图1(d)所示)。我们应用这种制造方法开发出了所需要的沟槽形貌结构(如图1(e)所示),实现了沟槽底部氧化硅薄膜厚度比沟槽侧壁厚的沟槽栅结构(如图1(f)所示)。

2)互连与金属化形貌结构的开发

我们使用氧化硅薄膜作为金属层与器件层之间的层间绝缘膜。通过刻蚀和热处理,形成接触孔,淀积金属,形成互连,之后再刻蚀金属形成电极(如图2(b)所示),最后在金属层之上形成钝化层,并开出键合孔。

图2 互连与金属化形貌结构(发射极金属互连)

图2 互连与金属化形貌结构(发射极金属互连)

2.2 器件终端形貌结构的开发

我们采用复合场限环和复合场板构成的复合耐压环作为器件终端结构,复合场限环由轻掺杂的场限环和重掺杂的场限环通过刻蚀出的耐压环窗口自对准掺杂复合而成,复合场板由掺杂多晶硅场板(如图3 所示)和金属场板复合而成,金属场板与场限环通过衬底接触孔相连接,金属场限环也通过接触孔与掺杂多晶硅场板连接,场板之上为钝化层。通过采用复合耐压环结构,可在满足器件耐压要求的同时减小芯片尺寸。

图3 终端形貌结构(多晶硅场板)

图3 终端形貌结构(多晶硅场板)

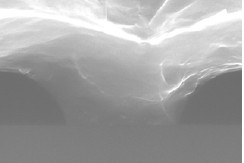

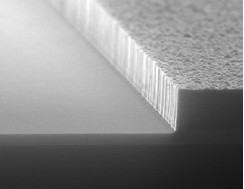

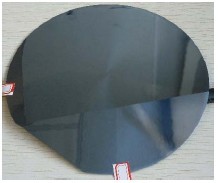

2.3 超薄片的实现与超薄片工艺加工

为实现器件的场终止结构,需要进行超薄片的加工,包括硅片的超薄化减薄,和对超薄硅片的湿法处理、离子注入、退火和金属化等加工。我们首先将特殊的蓝膜贴于硅片的表面,从硅片背面将硅片减薄到120 微米左右(如图4 所示),然后进行背面湿法腐蚀去除研磨损伤层,改善应力和表面粗糙度,并去除蓝膜。之后,利用我们提出的一种新型的超薄片加工方法,实现超薄片的背面离子注入加工,通过掺杂形成场终止的杂质分布结构。该超薄片的制造方法采用粘接材料和衬片,将粘接材料连续均匀地涂抹在衬片平边和平边两侧上表面的周边区域,再将待加工的超薄片的表面粘贴在衬片的上表面上,并保持平边对齐,之后可用常规的离子注入设备对超薄片的背面进行离子注入,注入完成后,将超薄片从衬片上表面分离,最后将超薄片和衬片上的粘接材料去除干净。完成超薄片的背面离子注入后,再进行注入退火,清洗和背面金属化。这样加工出来的超薄硅片可用于实现器件的场终止结构,降低饱和压降,提高器件性能。

图4 120 微米的超薄片

图4 120 微米的超薄片

3 器件形貌结构开发过程中遇到的问题与对策

在沟槽栅FS-IGBT 器件形貌结构开发过程中,也发生了一些问题。通过对这些问题发生的原因进行分析,确定并实施了相应的对策,确保了形貌结构开发的成功。

3.1 沟槽栅结构开发过程中发生的问题与对策

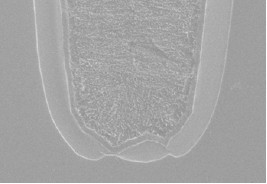

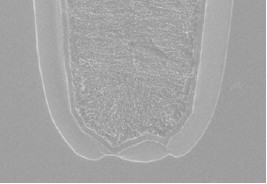

在完成沟槽栅多晶硅淀积之后,我们对沟槽的剖面形貌进行了切片分析,发现存在沟槽底部氧化异常(如图5 所示)等问题。

图5 沟槽栅结构异常形貌(沟槽底部氧化异常)

图5 沟槽栅结构异常形貌(沟槽底部氧化异常)

在前述用反应离子刻蚀(RIE)方法去除沟槽底部和沟槽外硅片表面上层的氮化硅薄膜之后,会在硅片表面留下一层反应生成聚合物(Polymer),如果该聚合物没有去除干净,会对后续工序甚至器件性能产生影响。特别地,当沟槽底部聚合物未去除干净时,会导致沟槽LOCOS 形成时底部氧化异常,不能形成圆滑的底部轮廓和需要的氧化膜厚度。在反应离子刻蚀之后,我们采用了特别的聚合物去除工艺,确保了沟槽底部LOCOS 正常形成。

3.2 其它问题与对策

这里主要讨论了终端结构与超薄片工艺开发过程中发生的形貌结构问题。

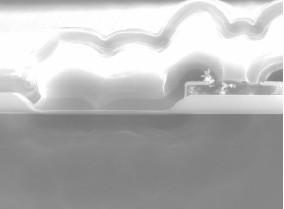

1)终端形貌结构开发过程中发生的问题与对策

在终端结构的开发过程中,发生了终端场限环上接触孔开孔不良(如图6 所示)等问题。

图6 (终端场限环上接触孔开孔不良)

图6 (终端场限环上接触孔开孔不良)

终端场限环上接触孔开孔不良导致了产品的耐压不良,开孔不良的原因主要是由于该处特殊的形貌结构使得在该处孔光刻涂胶后,曝光与显影未能将孔打开,从而发生该处孔刻蚀加工后部分接触孔未刻开或者全部未刻开异常。

2)超薄片工艺开发过程中发生的问题与对策在超薄片加工方面,发生了碎片(如图7 所示)等问题。

图7 超薄片碎片异常

图7 超薄片碎片异常

薄片碎片主要发生在背面离子注入工序,从图7 所示碎片发生的位置我们可以看出,导致碎片发生的应力集中在硅片平边附近,原因主要是机械应力和抽真空过程。通过采用前述的新型超薄片加工方法,基本上可以防止碎片的发生。

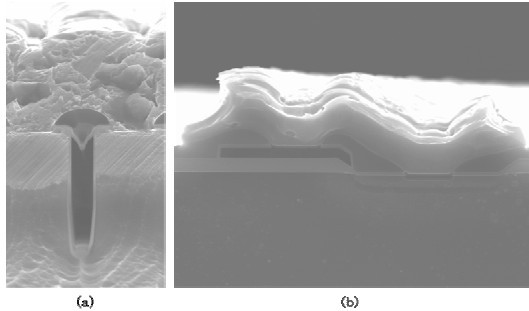

通过前面的研发和对所发生问题的对策,我们开发出了所需要的器件元胞形貌结构(如图8(a)所示)和器件终端形貌结构(如图8(b)。

图8 开发出的元胞形貌结构与终端形貌结构(无钝化层,(a)元胞形貌结构,(b)终端形貌结构)

4 结 论

我们开发了用于沟槽栅FS-IGBT 器件的形貌结构。在开发过程中,我们提出了一种新型的沟槽栅制造方法和一种新型的超薄片加工方法,开发出了所需要的沟槽栅形貌结构和超薄硅片;也开发了由复合场限环和复合场板构成的复合耐压环终端结构;在开发过程中也发生了一些问题,通过对这些问题发生的原因进行分析,确定并实施了相应的对策,确保了形貌结构开发的成功。

参考文献:

【1】 山上 倖三等,“トランジスタ”,特公昭47-21739,昭和47 年(1972)6 月19 日

【2】 B. J. Baliga, “Enhancement and Depletion Mode Vertical Channel MOS Gated Thyristors”,Electronics Letters,Vol.15,pp.645-647,September 27,1979

【3】 H. W. Becke et al., “POWER MOSFET WITH AN ANODE REGEON”, United State Patent,4,364,073,Dec.14,1982

【4】 “C. Frank Wheatley, Jr., BSEE”. Innovation Hall of Fame at A. James Clark School of Engineering

【5】 B. J. Baliga, “Fast Switching Insulated Gate Transistors”, IEEE Electron Device Letters,Vol.4,pp.452-454,1983

【6】 A. Nakagawa et al., “Non-Latch-Up 1200V 75A Bipolar-Mode MOSFET with Large ASO”, IEEE International Electron Devices Meeting Technical Digest,pp.860-861,1984

【7】 A. Nakagawa et al.,“CONDUCTIVITY MODULATED MOSFET”, United State Patent,4,672,407, Jun.9,1987

【8】 二宫 英彰等, “拡大する応用分野に対応して改善を続けるIGBT”, 東芝レビュー, Vol. 65, No.1,pp.15-18,2010 特集

【9】 H. R. Chang et al., “Insulated gate bipolar transistor (IGBT) with a trench gate structure”, IEEE Electron Devices Meeting,Vol.33,pp.674-677,1987

【10】 G. Miller et al., “A new concept for a non punch through IGBT with MOSFET like switching characteristics”, Power Electronics Specialists Conference,Vol.1,pp.21-25,1986

【11】 T. Laska et al., “The Field Stop IGBT (FS IGBT). A new power device concept with a great improvement potential”, IEEE Proceedings. of the 12th International Symposium on Power Semiconductor Devices and ICs,pp.355-358,2000

【12】 S. Dewar et al., “Soft Punch Through (SPT) – Setting new Standards in 1200V IGBT”, PCIM Nuremberg, June 2000

【13】 M. Rahimo et al., “Next Generation Planar IGBTs with SPT+ Technology”, Power Electronics Europe Magazine, Issue 6,September 2005

【14】 K. Nakamura et al., “Advanced wide cell pitch CSTBTs having light punch-through (LPT) structures”, IEEE Proceedings. of the 14th International Symposium on Power Semiconductor Devices and ICs,pp.277-280,2002

【15】 B. Zhang, “Power Semiconductor Devices and Smart Power ICs (Third Edition)”, Chapter 2, pp.12-57,2007

【16】 袁寿财,“IGBT 场效应半导体功率器件导论”,第9 章,pp.175-205,2008